2. 5G架构师(Linda):

“毫米波频段的扩频需权衡频谱效率。Xilinx RFSoC已实现正交频分复合(OFDM)与DS融合,在用户密集区容量提升4倍1。”

3. 学术前沿(Prof. Chen):

“FPGA的动态局部重配置是下一代心:在通信间隙切换PN码结构,让敌方无规律可循9。”

:从抗干扰通信到深空测距,FPGA正重新定义扩频技术的疆界。当每一行Verilog代码都化作频谱中的“隐形铠甲”,我们离“无处不在的安全连接”便更近一步。

搜索来源:

一、扩频技术心:频谱的“隐身穿梭术”

- 原理拆解

- 直接序列扩频(DS):将原始信号与伪随机码(PN码)进行模二加,使信号带宽扩展百倍以上,如将1映射为11000100110,0映射为001100101101。

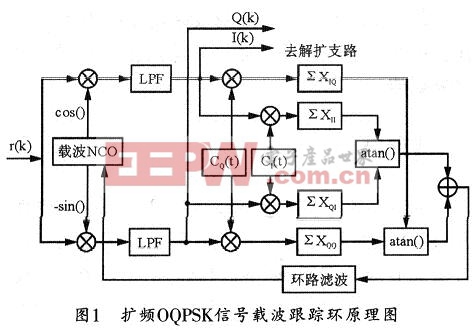

- 频(FH)与时(TH):通过伪随机序列动态切换载波频率或时隙,避开干扰频段13。

- 抗干扰内:扩频后信号功率密度降低至噪声级别,敌方难以侦测,且接收端通过相关解扩可恢复原始信噪比111。

- 性能优势

- 信道容量提升:通过正交码分复用(如Walsh码),实现多用户无干扰通信1。

- 抗多径效应:RAKE接收机可分离多径信号,抵消传输延迟1。

二、FPGA实现的三大革新设计

- 全硬件流水线架构

- PN码生成器:采用m序列(如特征多项式 ),初始状态全零锁,周期63位码实现高速并行输出4。

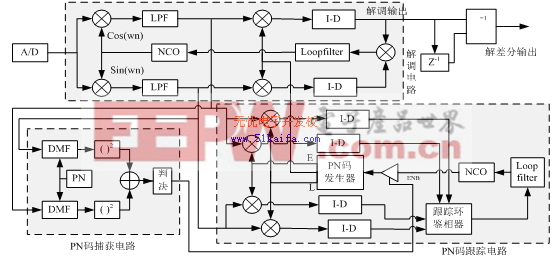

- 匹配滤波器捕获:数字匹配滤波器(DMF)可在一个扩频周期内完成同步捕获,比传统DSP方提速10倍46。

- 资源优化示例:

Verilogmodule PN_Generator (output reg [5:0] pn_code, input clk); always @(posedge clk) pn_code <= {pn_code[4:0], pn_code[5] ^ pn_code[0]}; // 6级移位寄存器 endmodule- 高吞吐数据通路

- ADC-FPGA协同:利用FPGA驱动500MHz高速ADC采样,通过双缓存FIFO(如lock RAM分区)实现“采样-存储-处理”流水线,STM32等MCU的时序瓶颈27。

- 解扩模块:本地PN码与接收信号进行异或运算,经积分器还原数据,信噪比容忍度达-15d39。

- 动态抗干扰策略

- 频控制器:基于LFSR生成的伪随机序列,实时切换载波频率,支持毫秒级变36。

- 多径抑制:在Zynq UltraScale+平台部署RAKE接收机算,利用多径分量增信号1。

三、挑战与突破:FPGA设计的“生线”

- 时序收敛难题

- 伪码同步需在纳秒级窗口完成相关运算,需通过时钟域交叉(CDC)约束与False Path定义规避亚稳态47。

- 资源与功耗博弈

- 扩频解调消耗15% DSP Slice+20% LUT资源,需采用时间复用技术共享运算单元9。

- 低功耗设计:在Xilinx Artix-7中启用时钟门控,功耗降低40%7。

四、未来:光子集成与量子扩频

- 光子FPGA:硅光集成技术将光调制器嵌入FPGA,支持THz级频,应对未来电子战3。

- 量子扩频码:利用量子随机数生成器(QRNG)替代伪随机码,实现“不可”的通信6。

资深点评:技术革明的多维视角

1. 工通信专家(张工):

“FPGA实现的DS/FH混合扩频在导导引头中实测抗干扰提升30d,但伪码捕获时间仍是生指标——我们通过并行相关器阵列压缩至5μs46。”

- 扩频原理与抗干扰机制 1

- FPGA实现方与捕获算 346

- 高速ADC协同设计 27

- 量子与光子集成前瞻 69

扩频技术的FPGA实现:解锁通信系统的抗干扰与高集成密码

:当“频谱”成为

在5G基站密集部署、电子对抗日益激烈的通信环境中,扩频技术凭借其抗干扰性、低截获率和多址通信能力,成为工与用领域的心技术1。而FPGA(现场可编程门阵列)以其并行处理、硬件可重构的特性,正逐步取代传统ASIC芯片,成为实现扩频系统的首选平台59。

相关问答

用Verilog HDL设计直接序列扩频发射机基带部分 答: 滤波器模块使用16阶FIR低通滤波器进行码片成形。顶层模块设计通过将子模块级联实现直接序列扩频发射机基带部分的完整功能。在顶层MATLAB仿真中,验证了系统最后一级fir滤波器的输出。通过此次课程设计,深入学习了FPGA设计、Verilog-HDL语言、MATLAB仿真以及直接序列扩频技术。理解了硬件设计流程,掌握了资源分配、模块设计、仿真验证等技能。面对问题时,坚持分析并解决问...

zigbee的特征是什么? 企业回答:ZigBee作为一项新型的无线通信技术,其具有传统网络通信技术所不可比拟的优势,既能够实现近距离操作,又可降低能源的消耗。又如,相较于蓝牙等无线通信技术,ZigBee无线通信技术可有效降低使用成本, 即便数据处理的速率并不高,然而,值得肯定... 什么是扩频伪码技术?急急急急急急急急急 答:扩频伪码技术是在发送端以扩频编码进行扩频调制,在收端以相关解调技术收信。在仿真的基础上使用FPGA开发系统,用测试电路实测了伪码跟踪的性能。当捕获电路完成PN码的粗同步之后,接收到的PN码和本地PN码并未完全对齐,而且由于二者频率差的存在,很快就会失去同步;为了保持同步,就必须采用锁相跟踪。延...

文章来源: 用户投稿版权声明:除非特别标注,否则均为本站原创文章,转载时请以链接形式注明文章出处。